Article ID: 1000-7032(2012)11-1258-06

# The Stability of IGZO-TFT with Reactive Sputtered $SiO_x$ Insulator under White Light Illumination

LI Jun<sup>1,2\*</sup>, ZHOU Fan<sup>1</sup>, ZHANG Jian-hua<sup>2</sup>, JIANG Xue-yin<sup>1</sup>, ZHANG Zhi-lin<sup>1,2</sup>

(1. Department of Materials Science, Shanghai University, Shanghai 201800, China;

2. Key Laboratory of Advanced Display and System Applications, Ministry of Education, Shanghai University, Shanghai 200072, China)

\* Corresponding Author, E-mail: lijun\_yt@163.com

**Abstract**: We systematically investigated the stability of gallium indium zinc oxide (IGZO) thin film transistor (TFT) with reactive sputtered  $SiO_x$  insulator under white light illuminaion. The research involved an overall stress conditions that included light stress (LS), negative voltage stress (NBS), positive voltage stress (PBS), negative bias-light stress (NBLS), and positive bias-light stress (PBLS). The results demonstrate a large threshold voltage shift under LS and NBLS conditions, and a negligible threshold voltage shift under PBLS condition. The *C-V* characteristics indicated that the shift of threshold voltage came from traps generated at or near the dielectric/semiconductor interface. Additionally, the stretched exponential model was used to obtain the relaxation time. This work aimed to provide an instability origin of IGZO-TFT under white light illumination and gate voltage bias.

**Key words**: thin film transistor; stability; reactive sputtered  $SiO_x$ **CLC number**: 0472.4 **Document code**: A **DOI**: 10.3788/fgxb20123311.1258

# 用反应溅射法沉积 SiO<sub>x</sub> 绝缘层的 InGaZnO-TFT 的光照稳定性

李 俊<sup>1,2\*</sup>,周 帆<sup>1</sup>,张建华<sup>2</sup>,蒋雪茵<sup>1</sup>,张志林<sup>1,2</sup>

(1. 上海大学 材料科学与工程学院,上海 200072;

2. 上海大学 新型显示技术与应用集成教育部重点实验室,上海 200072)

**摘要:**制备了基于反应溅射 SiO<sub>x</sub> 绝缘层的 InGaZnO-TFT,并系统地研究了 InGaZnO-TFT 在白光照射下的稳定性,主要涉及到光照、负偏压、正偏压、光照负偏压和光照正偏压 5 种情况。结果表明,器件在光照和负偏压光照下的阈值偏移较大,而在正偏压光照情况下的阈值偏移几乎可以忽略。采用 *C-V* 方法证明阈值电压漂移是源于绝缘层/有源层附近及界面处的缺陷。另外,采用指数模式计算了缺陷态的弛豫时间。本研究的目的就是揭示 InGaZnO-TFT 在白光照射和偏压下的不稳定的原因。

关键 词:薄膜晶体管;稳定性;反应溅射 SiO<sub>x</sub>

收稿日期: 2012-07-01;修订日期: 2012-09-20

基金项目:国家自然科学基金(61274082,61077013,60777018,60776040);国家"863"计划(2010AA3A337,2008AA03A336);中国博士后基金(2012T50387,2011M500569)资助项目

作者简介: 李俊(1981 - ), 男, 安徽安庆人, 主要从事光电器件方面的研究。 E-mail: lijun\_yt@163.com

### 1 Introduction

Gallium indium zinc oxide (IGZO) thin film transistors (TFTs) have received much attention due to their potential application in active matrix liquid crystal displays (AM-LCDs), and active matrix organic light emitting diodes (OLEDs)<sup>[14]</sup>. Recently. the mobility of IGZO-TFT has improved significantly and reached a value of more than 5 cm<sup>2</sup>  $\cdot$  V<sup>-1</sup>  $\cdot$  s<sup>-1[5]</sup>. Although the mobility of IGZO-TFT is acceptable, the poor stability of IGZO-TFT is becoming a restricting factor in practical application. Some groups have studied the stability of IGZO-TFT under constant positive/negative gate bias<sup>[6-7]</sup>. However, in a real working AMLCD panel, the devices are inevitably exposed to white light illumination emanating from the backlight unit, and the switching TFTs always adopt a negative gate bias to maintain the "off" state of the pixel, thus it is necessary to maintain the stability under negative bias-light stress. In addition, the driving TFTs operate for a long period under simultaneous application of a positive gate bias and light illumination, so it is also important to study the stability under positive bias-light stress. Some studies have already reported the effect of illumination on amorphous IGZO-TFT under bias stress<sup>[8-9]</sup>. However, a systematic study is rather sparse. Because it involves an overall stress condition including light stress (LS), negative voltage stress (NBS), positive voltage stress (PBS), negative bias-light stress (NBLS), and positive bias-light stress (PBLS). Furthermore, few reports are quantitatively explained the origin of instability using C-V method.

In this work, IGZO-TFT with reactive sputtered  $SiO_x$  insulator under the different stress conditions (LS, NBS, PBS, NBLS, and PBLS) has been examined. The origin of instability is analyzed using the high-frequency (1 MHz) normalized *C-V* measurements of the IGZO MIS capacitors.

#### 2 Experiments

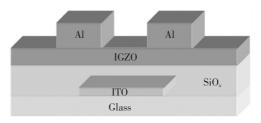

The cross section of the IGZO-TFT was shown schematically in Fig. 1. Prior to the different  $SiO_x$ films deposition on ITO glass, the ITO glass was cleaned with acetone, ethanol, and de-ionized water in that order. The sheet resistance of the ITO film was 30  $\Omega/\Box$ . Reactive sputtered SiO<sub>x</sub> film was deposited at room temperature with a mixture of high purity Ar and  $O_2$  (Ar/ $O_2$  flow ratio of 65/35). The target was Si (99.99%, 5.08 cm(2 in)). The forward power was kept at 100 W and the chamber pressured was held at 0.6 Pa. Following this, 40 nm of IGZO was deposited at room temperature via radio frequency (RF) magnetron sputtering to form the active layer. The sputtering was carried out in an argon (Ar) atmosphere at 1.2 Pa and a power of 50 W using a ceramic IGZO target (n(In):n(Ga):n(Zn) = 1:1:1, molar ratio). A 60-nm-thick Al film was sequentially vacuum deposited onto IGZO layer using a metal mask to define transistors with channel width  $W = 1 000 \ \mu m$  and channel length  $L = 180 \mu m$ . Finally, the sample was subjected to thermal annealing at 250 °C for 30 min.

The current-voltage characteristics of the devices were measured by using an Agilent E3647A Dual output DC power supply and a Keithley 6485 Picoammeter. The capacitance measurements were conducted with a HP 4284A Precision LCR meter. The thickness of SiO<sub>x</sub> gate insulator was determined by a surface profiler (Alpha-Step IQ). All measurements were carried out in air ambiance at room temperature.

Fig. 1 Schematic structure of the IGZO-TFT

# 3 Results and Discussion

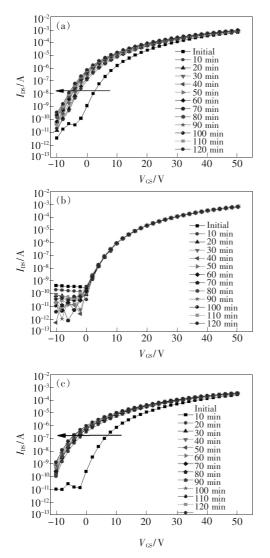

Fig. 2 (a), (b) and (c) are the transfer characteristics of devices subjected to light stress (LS), positive bias-light stress (PBLS) and negative biaslight stress (NBLS), respectively. A white light intensity of 10 000 lx is performed for 2 h, and the positive and negative bias stress are +10 V and

Fig. 2 Transfer characteristics of IGZO-TFT subjected to 10 000 lx white light illumination under (a) without gate bias stress, (b)10 V gate bias stress, and (c) -10 V gate bias stress.

-10 V, respectively.  $V_{\rm GS}$  is swept from -10 V to +50 V with the application of  $V_{\rm DS} = 30$  V. The saturation mobility  $(\mu_{\rm sat})$  is extracted from a linear fitting to the  $(I_{\rm DS})^{1/2}$ - $V_{\rm GS}$  curve, based on the equation  $I_{\rm DS} = (\mu_{\rm sat} C_{\rm ox} W/2L) (V_{\rm GS} - V_{\rm th})^2$ , where  $V_{\rm th}$  is the threshold voltage estimated from the intercept of the extrapolated curve with the voltage axis. The initial performance of the device without illumination is characterized in the dark environment. The device exhibits excellent electrical properties of  $\mu_{\rm sat} = 18.7$ cm<sup>2</sup> · V<sup>-1</sup> · s<sup>-1</sup>,  $V_{\rm th} = 15.3$  V, and  $I_{\rm on}/I_{\rm off} = 1.8 \times$ 10<sup>8</sup>. During illumination, the threshold voltage shifts to more negative direction with the increasing

illumination time. After 7 200 s continuous illumination with a 10 000 lx white light, the  $\mu_{sat}$  and  $V_{th}$  value are reduced to 15.6 cm<sup>2</sup>  $\cdot$  V<sup>-1</sup>  $\cdot$  s<sup>-1</sup> and 7.1 V, respectively. From Fig. 2 (a), it is easily seen that the  $I_{\rm off}$  value increases with the increase of illumination time due to more photo-generated charges. The device shows a large negative  $V_{\rm th}$  shift about -8.2 V after 7 200 s white light illumination, and the tendency of  $V_{\rm th}$  shift increases gradually with increasing illumination time. Recently, T. C. Chen et  $al^{[10]}$ have reported a plausible mechanism for the  $V_{\rm th}$  instability under illumination condition, in which the holes generated from light induced electron-hole pairs that react with the preabsorbed  $O_2^-$  to reduce into  $O_2$ , resulting in a negative  $V_{\rm th}$  shift. Compared with the transfer characteristics under LS condition, the threshold voltage of the device under NBLS shows a smaller value. However, the device under PBLS condition shows a better stability than that under LS condition. The saturation mobility of the device under PBLS almost remains unchanged.

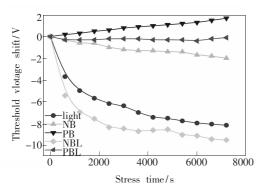

To further probe the instability of IGZO-TFT with reactive sputtered  $SiO_x$  insulator, Fig. 3 compares the threshold voltage shift of devices subjected to light stress (LS), negative voltage stress (NBS), positive voltage stress (PBS), negative bias-light stress (NBLS), and positive bias-light stress (PBLS). After gate bias stress for 7200 s, a positive shift of  $(\Delta V_{\rm th} \approx 1.8 \text{ V})$  for positive gate bias stress ( $V_{\rm GS} = 10$  V) and a negative shift ( $\Delta V_{\rm th} \approx -2$  V) for negative gate bias stress ( $V_{GS} = -10$  V) are obtained. The application of positive/negative bias stress to the gate causes redistributions in the trapped charge of the active layer in the IGZO-TFT. The device under NBLS condition shows a large  $V_{\rm th}$ shift of -9.7 V, which is much larger than  $V_{\rm th}$  shift of the device under NB condition. When a negative gate voltage ( $V_{GS} = -10$  V) is applied under illumination conditions, the illumination induces photoexcitation of valence band electrons into midgap states. Simultaneously, it will generates free hole carriers in the valence. Such free holes in the valence band will be attracted to the SiO\_/IGZO interface by the negative gate field and become trapped at

Fig. 3 Graph of the threshold voltage shift with respect to stress time

the interfacial energy states or injected into the  $SiO_x$ layer leading to negative  $V_{th}$  shift of the IGZO-TFT.

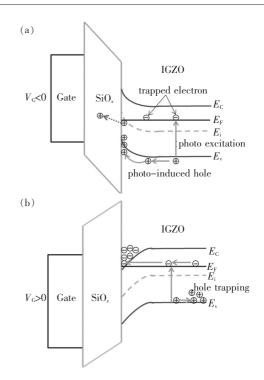

The schematic band diagram is shown in Fig. 4 (a). Negative stress depletes the trapped charge between  $E_{\rm F}$  and the conduction band, causing the Fermi level to be slightly shifted towards the conduction band. Therefore, the application of  $V_{\rm CS}$  easily shifts the  $E_{\rm F}$  to the conduction band, remaining fixed by the band-tail states. However, when the positive bias stress is applied under the same light illumination, the threshold voltage shift of IGZO-TFT under PBLS condition is only -0.2 V, which is much smaller than that of IGZO-TFT under LS condition (-9.5 V). It illustrates that the positive bias stress can suppress the negative  $V_{\rm th}$  shift. On the contrary, the illumination can suppress the positive  $V_{\rm th}$  shift. It suggests that the generated electron in the channel layer drifts toward the channel/insulator interface under the positive voltage and accumulated near the interface. At the same time, the positive gate field repels most of the photo-generated holes away from the gate insulator. The electrons and positive charges newly generated by light illumination under the positive gate bias seem to recombine very quickly under high drain-source current, as shown in Fig. 4(b), resulting in less  $V_{\rm th}$  shift. Similar results have been reported by other groups<sup>[11]</sup>. It also verifies the fact

Fig. 4 Energy band diagrams of the IGZO-TFT under (a) negative bias-light stress, and (b) positive bias-light stress.

that illumination can excite the trapped charges and accelerated the charge de-trapping process<sup>[12]</sup>.

The relationship between  $\Delta V_{\text{th}}$  and t is found to fit the stretched exponential model, which is originated from the negative charge being trapped at the channel/dielectric interface or getting injected into the gate dielectric<sup>[13-14]</sup>. A stretched exponential model can be described by the following equation:

$$|\Delta V_{\rm th}(t)| = |V_0| \left\{ 1 - \exp\left[-\left(\frac{t}{\tau}\right)^{\beta}\right] \right\},\tag{1}$$

where  $V_0 = V_{\rm GS} - V_{\rm th,0}$ ,  $V_{\rm th,0}$  is the threshold voltage at the start of the stress measurement.  $\beta$  is the stretched exponential exponent, and  $\tau$  reflects the characteristics carrier trapping time. The associated parameters are list in Table 1. The parameters indicate that carriers are easily injected into the gate insulator at the semiconductor/dielectric interface for

Table 1 Stretched exponential parameters under the different stress conditions

| Parameters | NBS                  | PBS                 | LS                  | NBLS                | PBLS                |

|------------|----------------------|---------------------|---------------------|---------------------|---------------------|

| $\tau/s$   | $1.05 \times 10^{5}$ | $6.8 \times 10^{5}$ | $8.6 \times 10^{3}$ | $7.6 \times 10^{3}$ | $3.5 \times 10^{6}$ |

| β          | 0.746                | 0.812               | 0.495               | 0.286               | 0.149               |

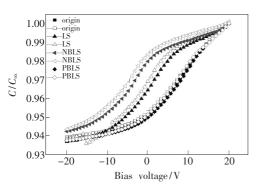

Fig. 5 Normalized *C-V* measurements of IGZO MIS capacitors under different stress

device under the negative bias illumination stress.

To further explain the charge trapping phenomenon, the high-frequency (1 MHz) normalized *C-V* measurements of the IGZO MIS capacitors with reactive sputtered SiO<sub>x</sub> is shown in Fig. 5. The voltage  $V_{\rm G}$ is swept from 20 V to -20 V and back to 20 V. A small and negligible hysteresis is observed for the device under positive bias-light stress or dark condition. However, the hysteresis width of  $\Delta V_{\rm G} = 1.2$  V is obtained for device under light stress. For the device under negative bias-light stress, the hysteresis width shows a bigger value of  $\Delta V_{\rm G} = 1.8$  V. The charge-trapping density  $(N_t)$  can be calculated by using the relation:  $N_t \cong [C_i (\Delta V_G)/q]$ , where  $C_i$  is the gate insulator capacitance and q is the elementary charge. The value of charge trapping is estimated to be 7.5 × 10<sup>10</sup> and 1.1 × 10<sup>11</sup> cm<sup>-2</sup> for the device under light stress and negative bias-light stress, respectively. It illustrates that the hysteresis effect may be attributed to the increasing of charges at/near IGZO/ SiO<sub>x</sub> interface or bulk trap under LS or NBLS condition.

## 4 Conclusion

In conclusion, the IGZO-TFT with reactive sputtered  $\text{SiO}_x$  insulator under the different stress conditions (LS, NBLS, and PBLS) has been examined. Light stress leads to a negative threshold voltage shift. Compared with the threshold voltage shift under LS, the threshold voltage shifts under NBLS are deteriorated and suppressed. *C-V* characteristics verifies that the instability of the device is attributed to the increasing of charges at/near IGZO/SiO<sub>x</sub> interface or bulk trap under light stress or negative bias-light stress.

#### References:

- [1] Arai T, Morosawa N, Tokunaga K, et al. Highly reliable oxide-semiconductor TFT for AM-OLED display [J]. SID Symposium Digest of Technical Papers, 2010, 41:1033-1036.

- [2] Lee J H, Kim D H, Yang D J, et al. World's largest (15-inch) XGA AMLCD panel using IGZO oxide TFT [J]. SID Symposium Digest of Technical Papers, 2008, 39:625-828.

- [3] Kim C J, Kim S, Lee J H, et al. Amorphous hafnium-indium-zinc oxide semiconductor thin film transistors [J]. Appl. Phys. Lett., 2009, 95(15):152103-1-3.

- [4] Li J, Zhou F, Lin H P, *et al.* Effect of N<sub>2</sub>O plasma treatment on the SiN<sub>x</sub>-based InGaZnO thin film transistors [J]. *Chin. J. Lumin.* (发光学报), 2012, 33(4):400-403 (in Chinese).

- [5] Zhou F, Zhang L, Li J, et al. Effect of Ta<sub>2</sub>O<sub>5</sub> thickness on the performances of ZnO-based thin film transistors [J]. Chin. J. Lumin. (发光学报), 2011, 32(2):188-192 (in English).

- [6] Moon Y K, Lee S, Kim W S, et al. Improvement in the bias stability of amorphous indium gallium zinc oxide thin-film transistors using an O<sub>2</sub> plasma-treated insulator [J]. Appl. Phys. Lett., 2009, 95(1):013507-1-3.

- [7] Nomura K, Kamiya T, Kikuchi Y, et al. Comprehensive studies on the stabilities of a-In-Ga-Zn-O based thin film transistor by constant current stress [J]. Thin Solid Film, 2010, 518(11):3012-3016.

- [8] Sung S Y, Choi J H, Han U B, et al. Effects of ambient atmosphere on the transfer characteristics and gate-bias stress stability of amorphous indium-gallium-zinc oxide thin-film transistors [J]. Appl. Phys. Lett., 2010, 96(1):102107-1-3.

- [9] Ryu B, Noh H K, Choi E A, et al. O-vacancy as the origin of negative bias illumination stress instability in amorphous In-Ga-Zn-O thin film transistors [J]. Appl. Phys. Lett., 2010, 97(2):022108-1-3.

- [10] Chen T C, Chang T C, Hsieh T Y, et al. Light-induced instability of an InGaZnO thin film transistor with and without

$SiO_x$  passivation layer formed by plasma-enhanced-chemical-vapor-deposition [J]. Appl. Phys. Lett., 2010, 97(19): 192103-1-3.

- [11] Park S H K, Ryu M, Yoon S M, et al. Light response of top gate InGaZnO thin film transistor [J]. Jpn. J. Appl. Phys., 2011, 50(3):03CB08-1-4.

- [12] Chen T C, Chang T C, Tsai C T, et al. Behaviors of InGaZnO thin film transistor under illuminated positive gate-bias stress [J]. Appl. Phys. Lett., 2010, 97(11):112104-1-3.

- [13] Lee J M, Cho I T, Lee J H, et al. Bias-stress-induced stretched-exponential time dependence of threshold voltage shift in InGaZnO thin film transistors [J]. Appl. Phys. Lett., 2008, 93(9):093504-1-3.

- [14] Wang L, Zhang G B, Qin X Y, *et al.* Self-assembly of SiO<sub>x</sub> novel nanostructures and their optical property [J]. *Chin. J. Lumin.* (发光学报), 2010, 31(3):390-394 (in Chinese).